## Verification Intellectual Property Products

# UART eVC

## e Verification Components

Globetech Solutions' eVCs are independent, pre-verified, re-usable, verification environments that can be readily integrated into your design.

Maintaining full compatibility with Cadence's Incisive Specman Simulator $^{\text{TM}}$ , these components provide a solid basis for forming and realizing a complete, reliable and re-usable verification strategy.

## e Reuse Methodology

Globetech Solutions' eVCs comply with Cadence's e Reuse Methodology ( $eRM^{TM}$ ). The eRM ensures that eVCs seamlessly plug-and-play and operate consistently with all eRM compliant verification environments by applying consistent terminology, architecture, coding style and packaging.

## ■ Why eVCs?

There are many advantages to choosing a Globetech Solutions *e* Verification Component:

- Time to silicon dramatically reduce the verification cycle

- Flexibility quickly create and fine tune a variety of test scenarios

- Risk Management pre-verified components help reduce problem space

- Re-usability spend your time creating new tests, not environments!

- Full Support integration, training and support to ensure your success

#### ▶ The UART eVC

The Universal Asynchronous Receiver Transmitter (UART) eVC is a powerful verification bundle built around the UART industry standard. Adopted by companies worldwide as a building block for reusable verification platforms, the UART eVC can be integrated in a variety of testing scenarios involving a processor and modem/network, making it ideal for embedded processor applications or system-on-chip environments.

#### Features

- ☑ Compatible with virtually any UART interface

- ✓ Written in e and fully compatible with Cadence Incisive Specman Simulator-HDL independent

- ☑ eRM compliant Plug-n-Play

- ✓ Includes executable verification plan for Incisive Verification Manager<sup>™</sup>

- ☑ Optimized for Incisive Scenario Builder<sup>™</sup>

- Interface-level: Can be used to verify the serial interface behavior of any UART device

- Serial interface agent provides constrainedrandom UART frame sequence generation with error injection

- ☑ Programmable serial interface characteristics with auto-flow support

- ☑ Independent monitor supports re-usability in different verification environments without loss of coverage

- ☑ Fault start bit and break indication detection

- Built-in metric analysis for Coverage-Driven Verification (CDV)

- ☑ Complete and configurable error reporting, adjustable levels of tracing and verbosity

- ☑ IrDA\* SIR frame encoding/decoding for UART-over-IrDA support [provided as separate module]

## UART eVC Structure

The UART *e*VC is a universal, highly reusable verification component, providing advanced capabilities for generating UART frames, driving and monitoring a UART interface, detecting errors and estimating functional coverage.

## Verification Using the UART eVC

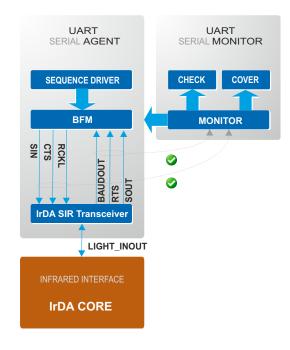

In **Figure 1**, the UART *e*VC is used to verify the serial interface of a UART device. The device could be a standalone IP core or part of a larger System on Chip design under test. In this scenario, the *e*VC's *serial agent* initiates constrained-random sequences to the DUT. The *monitor* examines traffic, scoreboards data and utilizes the *checker* to ensure adherence to the UART protocol. The *coverage* module onthe-fly tracks the functional aspects of the protocol that have been exercised. The *e*VC makes no assumptions as to the device's architecture or processor interface, making it applicable to virtually any type of UART.

## ▶ Benefits of the UART eVC

- ☑ **Universal solution:** A powerful verification environment which can be used with any UART device

- Solid technology: Built on best-of-breed technology and methodologies by Cadence Design Systems

- Proven quality: In strict compliance with industry quality standards

- High maturity: Used in many silicon-proven projects and a standard for many technology developers

- Maximum reuse: An eRM-compliant solution that guarantees reusability at the block, core and system levels

- Enhanced productivity: Optimized for the latest verification process management and control capabilities of Cadence Incisive Enterprise

#### ▶ Further Information

For further information or to request an evaluation, please visit us online at www.globetechsolutions.com or call us at +30 23 10 31 35 53.

| Component       | Function                                                                                                                              |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Serial<br>Agent | Emulates the corresponding functionality of the serial device attached to the UART DUT by injecting data and control stimuli.         |  |  |

| Monitor         | Tracks activity on the network side of the UART device. It also provides error checking, data scoreboarding and coverage information. |  |  |

Note that the monitor element is required for all testing scenarios; all other elements are entirely independent and can be deployed separately.

Table 1: Functional Description of UART eVC Components

**Figure 1: Verifying an SoC UART interface with the UART** *e***VC** The Serial Agent is used to drive frames into the UART interface. The Monitor is used to check bidirectional communication and score board data on both the transmit and receive paths (not shown here).

| Maturity  | First    | <i>e</i> RM | VPA      | SB        |

|-----------|----------|-------------|----------|-----------|

|           | Release  | Compliant   | Enabled  | Optimized |

| Excellent | Sep 2003 | <b>②</b>    | <b>Ø</b> | <b>Ø</b>  |

66 G.Viziynou St Thessaloniki 54636 Greece Tel: +30 23 10 31 35 53 Fax: +30 23 10 31 39 64 info@globetechsolutions.com www.globetechsolutions.com